# CS1W-HIO01/HCP22/HCA22 Customizable Counter Units

# **Programming Manual**

Produced January 2001

# Notice:

OMRON products are manufactured for use according to proper procedures by a qualified operator and only for the purposes described in this manual.

The following conventions are used to indicate and classify precautions in this manual. Always heed the information provided with them. Failure to heed precautions can result in injury to people or damage to property.

/!\ DANGER

Indicates an imminently hazardous situation which, if not avoided, will result in death or serious injury.

**!** WARNING

Indicates a potentially hazardous situation which, if not avoided, could result in death or serious injury.

(!) Caution

Indicates a potentially hazardous situation which, if not avoided, may result in minor or moderate injury, or property damage.

# **OMRON Product References**

All OMRON products are capitalized in this manual. The word "Unit" is also capitalized when it refers to an OMRON product, regardless of whether or not it appears in the proper name of the product.

The abbreviation "Ch," which appears in some displays and on some OMRON products, often means "word" and is abbreviated "Wd" in documentation in this sense.

The abbreviation "PC" means Programmable Controller and is not used as an abbreviation for anything else.

# Visual Aids

The following headings appear in the left column of the manual to help you locate different types of information.

**Note** Indicates information of particular interest for efficient and convenient operation of the product.

**Reference** Indicates supplementary information on related topics that may be of interest to the user.

1, 2, 3... 1. Indicates lists of one sort or another, such as procedures, checklists, etc.

# © OMRON, 2001

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or by any means, mechanical, electronic, photocopying, recording, or otherwise, without the prior written permission of OMRON.

No patent liability is assumed with respect to the use of the information contained herein. Moreover, because OMRON is constantly striving to improve its high-quality products, the information contained in this manual is subject to change without notice. Every precaution has been taken in the preparation of this manual. Nevertheless, OMRON assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained in this publication.

# TABLE OF CONTENTS

| PRECAUTIONS                                                            | • • |

|------------------------------------------------------------------------|-----|

| 1 Intended Audience                                                    |     |

| 2 General Precautions                                                  |     |

| 3 Safety Precautions                                                   |     |

| 4 Operating Environment Precautions                                    |     |

| 5 Application Precautions                                              |     |

| 6 Data Backup                                                          |     |

| 7 Conformance to EC Directives                                         |     |

| SECTION 1                                                              |     |

|                                                                        |     |

| Memory Areas                                                           | • • |

| SECTION 2                                                              |     |

| Instruction Set                                                        |     |

|                                                                        |     |

| 2-1 Instruction Tables                                                 |     |

| 2-2 Sequence Input Instructions                                        |     |

| 2-3 Sequence Output Instructions                                       |     |

| 2-4 Sequence Control Instructions                                      |     |

| 2-5 Timer and Counter Instructions                                     |     |

| 2-6 Data Shift Instructions                                            |     |

| 2-7 Data Movement Instructions                                         |     |

| 2-8 Comparison Instructions                                            |     |

| 2-9 Conversion Instructions                                            |     |

| 2-10 Data Control Instructions                                         |     |

| 2-11 Special Instructions                                              |     |

| 2-12 Symbol Math Instructions                                          |     |

| 2-13 Table Data Processing Instructions                                |     |

| 2-14 Special Math Instructions                                         |     |

| 2-15 Logic Instructions                                                |     |

| 2-16 Increment/Decrement Instructions                                  |     |

| 2-17 Subroutine Instructions                                           |     |

| 2-18 Interrupt Control Instructions                                    |     |

| 2-19 High-Speed Counter/Pulse Output Instructions                      |     |

| 2-20 I/O Instructions                                                  |     |

| 2-21 Step Instructions: STEP DEFINE and STEP START-STEP(08)/SNXT(09)   |     |

| 2-22 User Error Instructions:<br>FAILURE ALARM AND RESET – FAL(06) and |     |

| SEVERE FAILURE ALARM – FALS(07)                                        |     |

| Index                                                                  | 1   |

| Revision History                                                       | 1   |

# About this Manual:

This manual describes the memory areas and ladder programming instructions of the CS1W-HIO01, CS1W-HCP22, and CS1W-HCA22 Customizable Counter Units and includes the sections described below. The Customizable Counter Units provide both normal contact I/O points with special I/O points to provide ideal control capabilities for many applications. The Customizable Counter Units are classified as CS1 Special I/O Units.

Please read this manual and all other manuals for the Customizable Counter Units listed below carefully and be sure you understand the information provided before attempting to program and or operate a Customizable Counter Unit.

| Manual                                                                                      | Cat. No. | Contents                                                                                                                    |

|---------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| CS1W-HIO01/HCP22/HCA22<br>Customizable Counter Units<br>Programming Manual<br>(this manual) | W384     | Describes the memory areas and programming instructions of the Customizable Counter Units.                                  |

| CS1W-HIO01/HCP22/HCA22<br>Customizable Counter Unit<br>Operation Manual                     | W378     | Describes the hardware and software operation of the Customizable Counter Units.                                            |

| SYSMAC WS02-CXP□□-E<br>CX-Programmer<br>User Manual                                         | W361     | Provide information on how to use the CX-Programmer, a Windows-based Programming Device that supports the CQM1H-series PCs. |

| CQM1H Series<br>Programmable Controllers<br>Operation Manual                                | W363     | Describes Programming Console operations that can be used connected to the Customizable Counter Units.                      |

Section 1 describes the memory areas that can be used in the Customizable Counter Units.

Section 2 describes the ladder programming instructions that can be used in the Customizable Counter Units.

/!\WARNING Failure to read and understand the information provided in this manual may result in personal injury or death, damage to the product, or product failure. Please read each section in its entirety and be sure you understand the information provided in the section and related sections before attempting any of the procedures or operations given.

# **PRECAUTIONS**

This section provides general precautions for using the CS1W-HIO01, CS1W-HCP22, and CS1W-HCA22 Customizable Counter Units.

The information contained in this section is important for the safe and reliable application of the Customizable Counter Units. You must read this section and understand the information contained before attempting to set up or operate a Customizable Counter Unit.

| 1 Intended    | Audience                           | xii |

|---------------|------------------------------------|-----|

| 2 General P   | Precautions                        | xii |

| 3 Safety Pre  | ecautions                          | xi  |

| 4 Operating   | Environment Precautions            | xii |

| 5 Application | on Precautions                     | xiv |

| 6 Data Bacl   | kup                                | XV  |

| 6-1           | Automatic Backup                   | XV  |

| 6-2           | User Programming                   | XV  |

| 6-3           | Backing Up DM Area to Flash Memory | xvi |

| 7 Conforma    | ance to EC Directives              | xvi |

| 7-1           | Applicable Directives              | xvi |

| 7-2           | Concepts                           | xvi |

| 7-3           | Conformance to EC Directives       | xix |

3 Safety Precautions

#### Intended Audience 1

This manual is intended for the following personnel, who must also have knowledge of electrical systems (an electrical engineer or the equivalent).

- Personnel in charge of installing FA systems.

- Personnel in charge of designing FA systems.

- Personnel in charge of managing FA systems and facilities.

#### 2 General Precautions

The user must operate the product according to the performance specifications described in the operation manuals.

Before using the product under conditions which are not described in the manual or applying the product to nuclear control systems, railroad systems, aviation systems, vehicles, combustion systems, medical equipment, amusement machines, safety equipment, and other systems, machines, and equipment that may have a serious influence on lives and property if used improperly, consult your OMRON representative.

Make sure that the ratings and performance characteristics of the product are sufficient for the systems, machines, and equipment, and be sure to provide the systems, machines, and equipment with double safety mechanisms.

This manual provides information for programming and operating the Unit. Be sure to read this manual before attempting to use the Unit and keep this manual close at hand for reference during operation.

/! WARNING It is extremely important that a PC and all PC Units be used for the specified purpose and under the specified conditions, especially in applications that can directly or indirectly affect human life. You must consult with your OMRON representative before applying a PC System to the above-mentioned applications.

#### 3 **Safety Precautions**

/!\WARNING Do not attempt to take any Unit apart while the power is being supplied. Doing so may result in electric shock.

/!\ WARNING Do not touch any of the terminals or terminal blocks while the power is being supplied. Doing so may result in electric shock.

/!\WARNING Do not attempt to disassemble, repair, or modify any Units. Any attempt to do so may result in malfunction, fire, or electric shock.

/!\ WARNING Do not touch the Power Supply Unit while power is being supplied or immediately after power has been turned OFF. Doing so may result in electric shock.

/ WARNING Provide safety measures in external circuits, i.e., not in the Programmable Controller (CPU Unit including associated Units; referred to as "PC"), in order to ensure safety in the system if an abnormality occurs due to malfunction of the PC or another external factor affecting the PC operation. Not doing so may result in serious accidents.

- Emergency stop circuits, interlock circuits, limit circuits, and similar safety measures must be provided in external control circuits.

- The PC will turn OFF all outputs when its self-diagnosis function detects any

error or when a severe failure alarm (FALS) instruction is executed. As a countermeasure for such errors, external safety measures must be provided to ensure safety in the system.

- The PC outputs may remain ON or OFF due to deposition or burning of the output relays or destruction of the output transistors. As a countermeasure for such problems, external safety measures must be provided to ensure safety in the system.

- When the 24-VDC output (service power supply to the PC) is overloaded or short-circuited, the voltage may drop and result in the outputs being turned OFF. As a countermeasure for such problems, external safety measures must be provided to ensure safety in the system.

/! Caution

Execute online edit only after confirming that no adverse effects will be caused by extending the cycle time. Otherwise, the input signals may not be readable.

/ Caution

Confirm safety at the destination node before transferring a program to another node or changing contents of the I/O memory area. Doing either of these without confirming safety may result in injury.

**∕!** Caution

Tighten the screws on the terminal block of the AC power supply to the torque specified in the operation manual. The loose screws may result in burning or malfunction.

# 4 Operating Environment Precautions

/ Caution

Do not operate the control system in the following locations:

- · Locations subject to direct sunlight.

- Locations subject to temperatures or humidity outside the range specified in the specifications.

- Locations subject to condensation as the result of severe changes in temperature.

- Locations subject to corrosive or flammable gases.

- Locations subject to dust (especially iron dust) or salts.

- Locations subject to exposure to water, oil, or chemicals.

- Locations subject to shock or vibration.

**∕!**\Caution

Take appropriate and sufficient countermeasures when installing systems in the following locations:

- Locations subject to static electricity or other forms of noise.

- Locations subject to strong electromagnetic fields.

- Locations subject to possible exposure to radioactivity.

- Locations close to power supplies.

(!) Caution

The operating environment of the PC System can have a large effect on the longevity and reliability of the system. Improper operating environments can lead to malfunction, failure, and other unforeseeable problems with the PC System. Be sure that the operating environment is within the specified conditions at installation and remains within the specified conditions during the life of the system.

#### **Application Precautions** 5

/!\ WARNING Always heed these precautions. Failure to abide by the following precautions could lead to serious or possibly fatal injury.

- $\bullet$  Always connect to a ground of 100  $\Omega$  or less when installing the Units. Not connecting to a ground of 100  $\Omega$  or less may result in electric shock.

- $\bullet$  A ground of 100  $\Omega$  or less must be installed when shorting the GR and LG terminals on the Power Supply Unit.

- Always turn OFF the power supply to the PC before attempting any of the following. Not turning OFF the power supply may result in malfunction or electric

- Mounting or dismounting Power Supply Units, I/O Units, CPU Units, Inner Boards, or any other Units.

- Assembling the Units.

- Setting DIP switches or rotary switches.

- Connecting cables or wiring the system.

- Connecting or disconnecting the connectors.

Failure to abide by the following precautions could lead to faulty operation of the PC or the system, or could damage the PC or PC Units. Always heed these precautions.

- Always turn ON power to the PC before turning ON power to the control system. If the PC power supply is turned ON after the control power supply, temporary errors may result in control system signals because the output terminals on DC Output Units and other Units will momentarily turn ON when power is turned ON to the PC.

- Fail-safe measures must be taken by the customer to ensure safety in the event that outputs from Output Units remain ON as a result of internal circuit failures, which can occur in relays, transistors, and other elements.

- Fail-safe measures must be taken by the customer to ensure safety in the event of incorrect, missing, or abnormal signals caused by broken signal lines, momentary power interruptions, or other causes.

- Interlock circuits, limit circuits, and similar safety measures in external circuits (i.e., not in the Programmable Controller) must be provided by the customer.

- Always use the power supply voltages specified in the operation manuals. An incorrect voltage may result in malfunction or burning.

- Take appropriate measures to ensure that the specified power with the rated voltage and frequency is supplied in places where the power supply is unstable. An incorrect power supply may result in malfunction.

- Install external breakers and take other safety measures against short-circuiting in external wiring. Insufficient safety measures against short-circuiting may result in burning.

- Do not apply voltages to the Input Units in excess of the rated input voltage. Excess voltages may result in burning.

- Do not apply voltages or connect loads to the Output Units in excess of the maximum switching capacity. Excess voltage or loads may result in burning.

- Disconnect the functional ground terminal when performing withstand voltage tests. Not disconnecting the functional ground terminal may result in burning.

- Install the Units properly as specified in the operation manuals. Improper installation of the Units may result in malfunction.

- Be sure that all the mounting screws, terminal screws, and cable connector screws are tightened to the torque specified in the relevant manuals. Incorrect tightening torque may result in malfunction.

- Leave the label attached to the Unit when wiring. Removing the label may result in malfunction if foreign matter enters the Unit.

- Remove the label after the completion of wiring to ensure proper heat dissipation. Leaving the label attached may result in malfunction.

- Use crimp terminals for wiring. Do not connect bare stranded wires directly to terminals. Connection of bare stranded wires may result in burning.

- · Wire all connections correctly.

- Double-check all wiring and switch settings before turning ON the power supply. Incorrect wiring may result in burning.

- Mount Units only after checking terminal blocks and connectors completely.

- Be sure that the terminal blocks, Memory Units, expansion cables, and other items with locking devices are properly locked into place. Improper locking may result in malfunction.

- Check switch settings, the contents of the DM Area, and other preparations before starting operation. Starting operation without the proper settings or data may result in an unexpected operation.

- Check the user program for proper execution before actually running it on the Unit. Not checking the program may result in an unexpected operation.

- Confirm that no adverse effect will occur in the system before attempting any of the following. Not doing so may result in an unexpected operation.

- Changing the operating mode of the PC.

- Force-setting/force-resetting any bit in memory.

- Changing the present value of any word or any set value in memory.

- Resume operation only after transferring to the new CPU Unit the contents of the DM Area, HR Area, and other data required for resuming operation. Not doing so may result in an unexpected operation.

- Do not pull on the cables or bend the cables beyond their natural limit. Doing either of these may break the cables.

- Do not place objects on top of the cables or other wiring lines. Doing so may break the cables.

- When replacing parts, be sure to confirm that the rating of a new part is correct.

Not doing so may result in malfunction or burning.

- Before touching a Unit, be sure to first touch a grounded metallic object in order to discharge any static build-up. Not doing so may result in malfunction or damage.

- When transporting or storing circuit boards, cover them in antistatic material to protect them from static electricity and maintain the proper storage temperature.

- Do not touch circuit boards or the components mounted to them with your bare hands. There are sharp leads and other parts on the boards that may cause injury if handled improperly.

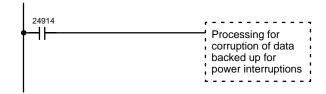

- Data in the DM Area, error history, EM Area, or Timer/Counter Area may become corrupted if power is not supplied for an extended period of time. Program the PC to check SR 24914 before starting operation. If SR 24914 is ON, the memory areas that are normally held during power interruptions will not have been held properly (i.e., the data will be corrupted). (The data in the DM Area can be backed up to flash memory by turning ON SR 25200.)

Data Backup 6

# 6 Data Backup

# 6-1 Automatic Backup

Data in the Customizable Counter Units is backed up either by a super capacitor or flash memory, as listed in the following table.

| Data                                                                                                                                                                                          | Data backup              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| DM Area (DM 0000 to DM 6143), EM Area (EM 0000 to EM 2047), error history (DM 6144 to DM 6199), and counter present values.                                                                   | RAM with super capacitor |

| A setting is provided to either enable or disable holding EM Area data. The default is to not hold the data.                                                                                  |                          |

| User program, read-only DM Area (DM 6200 to DM 6599), Unit Setup Area (DM 6600 to DM 6655), expansion instructions information, read/write portion of DM Area (DM 0000 to DM 6143, see note.) | Flash memory             |

**Note** The contents of DM 0000 to DM 6143 are written to flash memory only when SR 25200 (DM Area Backup Bit) is turned ON.

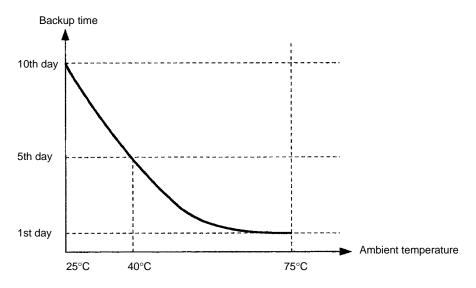

The data in RAM is backed up by the super capacitor for 10 days at 25°C. The backup time varies with the ambient temperature as shown in the following graph.

**Note** The times give above assume that the capacitor is completely charged. Power must be supply to the Unit for at least 15 minutes to completely charge the capacitor.

The data backed up by the capacitor will become unstable or corrupted if the backup time is exceeded.

# 6-2 User Programming

If the power supply is turned OFF for longer than the data backup time (10 days at 25°C), the data in the DM Area, EM Area, and Error Log, as well as counter present values, will be lost and any data that is read will be unstable.

If the power supply is to be turned OFF for an extended period of time, the contents of DM 0000 to DM 6143 can be backed up in flash memory. The Backup Data Corrupted Flag (SR 24914) can also be used as shown below to detect when backup data (i.e., data in the DM Area, EM Area, and Error Log, as well as

counter present values) has become corrupted to perform appropriate error processing.

DM 0000 to DM 6143 (read/write portion of DM Area) can be backed up in flash memory by the user as described in the next section.

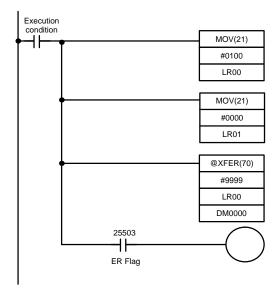

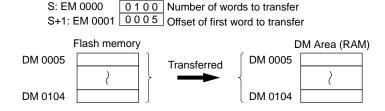

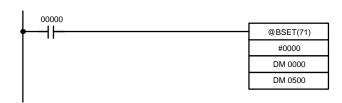

# 6-3 Backing Up DM Area to Flash Memory

The contents of DM 0000 to DM 6143 can be written to flash memory by turning ON SR 25200 (DM Flash Memory Backup Bit) in PROGRAM mode. (SR 25200 will turn OFF automatically when transfer has been completed.)

The data stored in flash memory can be read back to DM 0000 to DM 6143 by using the following type of programming.

# 7 Conformance to EC Directives

# 7-1 Applicable Directives

- EMC Directives

- Low Voltage Directive

# 7-2 Concepts

#### **EMC Directives**

OMRON devices that comply with EC Directives also conform to the related EMC standards so that they can be more easily built into other devices or machines. The actual products have been checked for conformity to EMC standards (see the following note). Whether the products conform to the standards in the system used by the customer, however, must be checked by the customer.

EMC-related performance of the OMRON devices that comply with EC Directives will vary depending on the configuration, wiring, and other conditions of the equipment or control panel in which the OMRON devices are installed. The customer must, therefore, perform final checks to confirm that devices and the overall machine conform to EMC standards.

**Note** Applicable EMC (Electromagnetic Compatibility) standards are as follows:

EMS (Electromagnetic Susceptibility): EN50082-2 EMI (Electromagnetic Interference): EN50081-2

(Radiated emission: 10-m regulations)

# **Low Voltage Directive**

Always ensure that devices operating at voltages of 50 to 1,000 VAC or 75 to 1,500 VDC meet the required safety standards for the PC (EN61131-2).

# 7-3 Conformance to EC Directives

The CS1W-HIO01, CS1W-HCP22, and CS1W-HCA22 Customizable Counter Units comply with EC Directives. To ensure that the machine or device in which a CS1W-HIO01, CS1W-HCP22, or CS1W-HCA22 Customizable Counter Unit is used complies with EC directives, the Unit must be installed as follows:

- **1, 2, 3...** 1. The CS1W-HIO01, CS1W-HCP22, and CS1W-HCA22 Customizable Counter Unit must be installed within a control panel.

- Reinforced insulation or double insulation must be used for the CS1W-HIO01, CS1W-HCP22, or CS1W-HCA22 Customizable Counter Unit DC power supplies used for the communications and I/O power supplies.

- 3. CS1W-HIO01, CS1W-HCP22, and CS1W-HCA22 Customizable Counter Units complying with EC Directives also conform to the Common Emission Standard (EN50081-2). When a CS1W-HIO01, CS1W-HCP22, and CS1W-HCA22 Customizable Counter Unit is built into a machine, however, changes can occur, particularly for the radiated emission (10-m regulations), due to the structure of the machine, other connected devices, wiring, etc. The customer must, therefore, perform final checks to confirm that devices and the overall machine using a CS1W-HIO01, CS1W-HCP22, or CS1W-HCA22 Customizable Counter Unit conform to EC standards.

# **SECTION 1 Memory Areas**

This section describes the memory areas that can be used in the Customizable Counter Units.

Memory Areas Section 1

The following memory areas can be used with the Customizable Counter Units. Addresses not listed in the following table cannot be used as operations in the ladder programming instructions for the Customizable Counter Units.

| Data area                           | Size                                           | Words                                              | Bits                                                                                                        | Function                                                                                                                                                |

|-------------------------------------|------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Area                          | Input Area 12 bits IR 000 IR 00000 to IR 00011 |                                                    | Bits in the Input Area are allocated to input terminals. These allocations are fixed and cannot be changed. |                                                                                                                                                         |

|                                     |                                                |                                                    |                                                                                                             | IR 00000 to IR 00003 can be used either as normal inputs or as interrupt inputs. Interrupt inputs are used in Input Interrupt Mode or Counter Mode.     |

| Output Area                         | 8 bits                                         | IR 001                                             | IR 00100 to IR 00107                                                                                        | Bits in the Output Area are allocated to output terminals. These allocations are fixed and cannot be changed.                                           |

|                                     |                                                |                                                    |                                                                                                             | IR 00108 to IR 00115 can also be used as work bits in programming.                                                                                      |

| Work Area                           | 1,088 bits                                     | IR 002 to IR 049                                   | IR 00200 to IR 04915                                                                                        | Work bits do not have any specific func-                                                                                                                |

|                                     |                                                | IR 200 to IR 219                                   | IR 20000 to IR 21915                                                                                        | tion, and they can be freely used within the program.                                                                                                   |

| SR Area                             | 568 bits                                       | SR 220 to SR 255                                   | SR 22000 to SR 25507                                                                                        | These bits serve specific functions such as flags and control bits.                                                                                     |

|                                     |                                                |                                                    |                                                                                                             | SR 230 to SR 239 are used to exchange data with the I/O memory in the CPU Unit.                                                                         |

| AR Area                             | 448 bits                                       | AR 00 to AR 27                                     | AR 0000 to AR 2715                                                                                          | These bits serve specific functions such as flags and control bits.                                                                                     |

| TR Area                             | 8 bits                                         |                                                    | TR 0 to TR 7                                                                                                | These bits are used to temporarily store ON/OFF status at program branches.                                                                             |

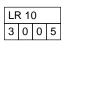

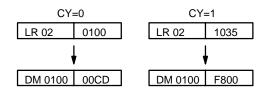

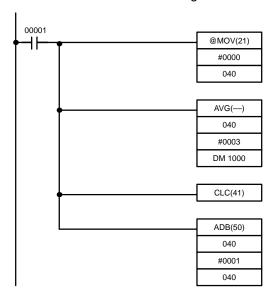

| LR Area                             | 256 bits                                       | LR 00 to LR 31                                     | LR 0000 to LR 3115                                                                                          | These bits are used to exchange data with the CPU Unit. Cyclic data transfers can be set up with user-specified words in the CPU Unit.                  |

|                                     |                                                |                                                    |                                                                                                             | Up to 32 I/O words of data can be exchanged. The settings for the LR Area links are made in DM 6601 to DM 6604 of the Customizable Counter Unit.        |

| Timer/Counter<br>Area               | 256 bits                                       | TIM/CNT 000 to TIM/CNT 255 (timer/counter numbers) |                                                                                                             | The timer numbers in the Timer/Counter Area are allocated to create timers and counters. The same numbers are used for both timers and counters.        |

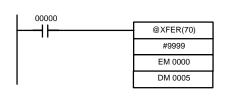

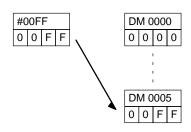

| Read/Write<br>portion of DM<br>Area | 6,144<br>words                                 | DM 0000 to DM 6143                                 |                                                                                                             | DM Area data can be read and written in word units only. Word values are retained when power is turned OFF or when the operating mode is switched.      |

|                                     |                                                |                                                    |                                                                                                             | The contents of the DM Area can be backed up in flash memory by turning on a control bit (SR 25200). Data can be read from flash memory using XFER(70). |

| EM Area                             | 2,048<br>words                                 | EM 0000 to EM 2047                                 |                                                                                                             | EM area data can be read and written in word units only.                                                                                                |

|                                     |                                                |                                                    |                                                                                                             | It is possible to set whether the EM Area is retained or cleared when power is turned OFF or when the operating mode is switched.                       |

# **SECTION 2 Instruction Set**

The Customizable Counter Units have a large programming instruction set that allows for easy programming for many applications. This section explains instructions individually and provides the ladder diagram symbol, data areas, and flags used with each.

| 2-1 | Instruct | ion Tables                                         |

|-----|----------|----------------------------------------------------|

|     | 2-1-1    | Instructions with Fixed Function Codes             |

|     | 2-1-2    | Expansion Instructions                             |

|     | 2-1-3    | Alphabetic List by Mnemonic                        |

| 2-2 | Sequen   | ce Input Instructions                              |

|     | 2-2-1    | LOAD, LOAD NOT, AND, AND NOT, OR, and OR NOT       |

|     | 2-2-2    | AND LOAD and OR LOAD                               |

| 2-3 | Sequen   | ce Output Instructions                             |

|     | 2-3-1    | OUTPUT and OUTPUT NOT – OUT and OUT NOT            |

|     | 2-3-2    | SET and RESET – SET and RSET                       |

|     | 2-3-3    | KEEP – KEEP(11)                                    |

|     | 2-3-4    | DIFFERENTIATE UP and DOWN – DIFU(13) and DIFD(14)  |

| 2-4 | Sequen   | ce Control Instructions                            |

|     | 2-4-1    | NO OPERATION – NOP(00)                             |

|     | 2-4-2    | END – END(01)                                      |

|     | 2-4-3    | INTERLOCK and INTERLOCK CLEAR – IL(02) and ILC(03) |

|     | 2-4-4    | JUMP and JUMP END – JMP(04) and JME(05)            |

| 2-5 | Timer a  | nd Counter Instructions                            |

|     | 2-5-1    | TIMER – TIM                                        |

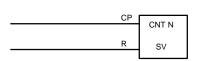

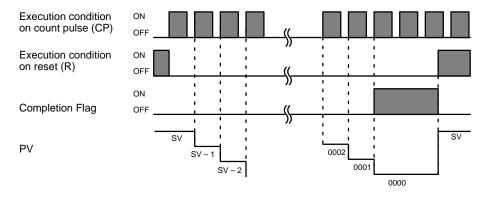

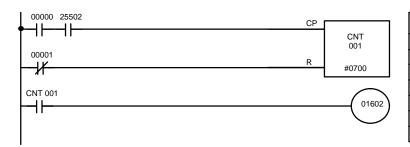

|     | 2-5-2    | COUNTER – CNT                                      |

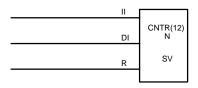

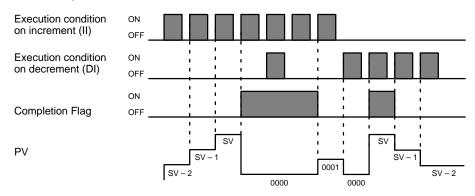

|     | 2-5-3    | REVERSIBLE COUNTER – CNTR(12)                      |

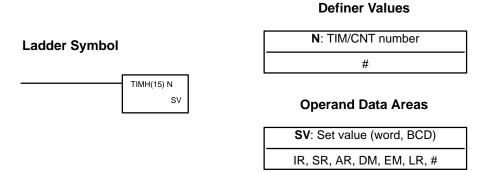

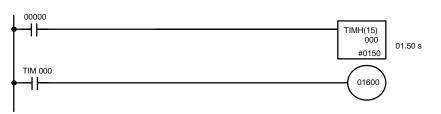

|     | 2-5-4    | HIGH-SPEED TIMER – TIMH(15)                        |

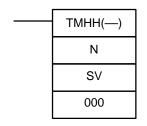

|     | 2-5-5    | ONE-MS TIMER – TMHH(—)                             |

| 2-6 | Data Sh  | nift Instructions                                  |

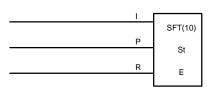

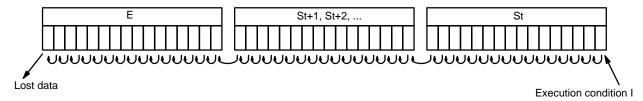

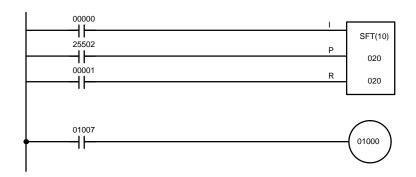

|     | 2-6-1    | SHIFT REGISTER – SFT(10)                           |

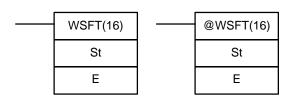

|     | 2-6-2    | WORD SHIFT – WSFT(16)                              |

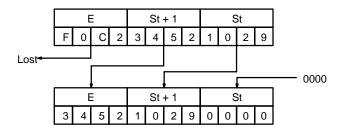

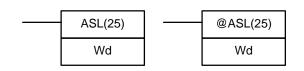

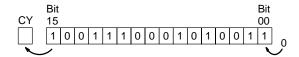

|     | 2-6-3    | ARITHMETIC SHIFT LEFT – ASL(25)                    |

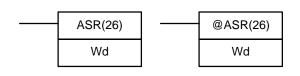

|     | 2-6-4    | ARITHMETIC SHIFT RIGHT – ASR(26)                   |

|     | 2-6-5    | ROTATE LEFT – ROL(27)                              |

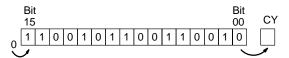

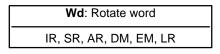

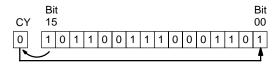

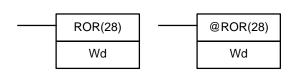

|     | 2-6-6    | ROTATE RIGHT – ROR(28)                             |

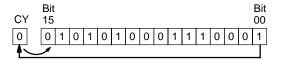

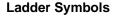

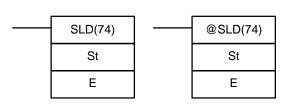

|     | 2-6-7    | ONE DIGIT SHIFT LEFT – SLD(74)                     |

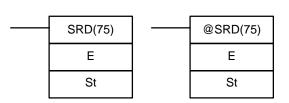

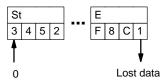

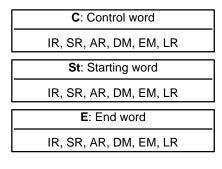

|     | 2-6-8    | ONE DIGIT SHIFT RIGHT – SRD(75)                    |

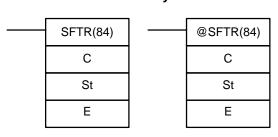

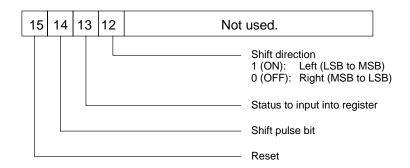

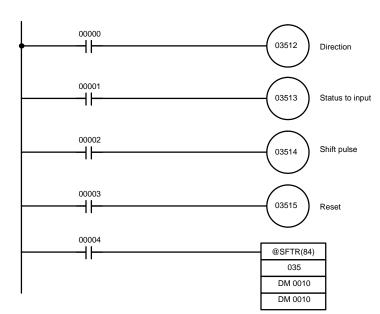

|     | 2-6-9    | REVERSIBLE SHIFT REGISTER – SFTR(84)               |

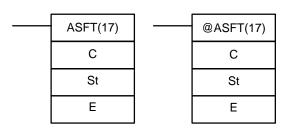

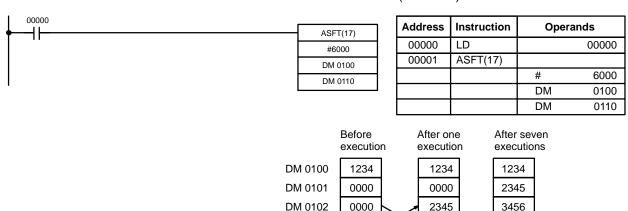

|     | 2-6-10   | ASYNCHRONOUS SHIFT REGISTER – ASFT(17)             |

| 2-7 | Data M   | ovement Instructions                               |

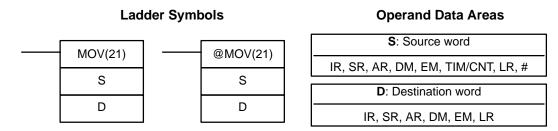

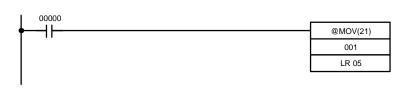

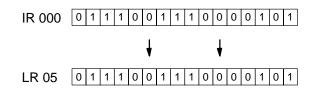

|     | 2-7-1    | MOVE – MOV(21)                                     |

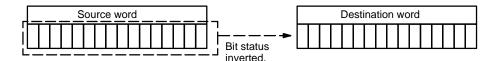

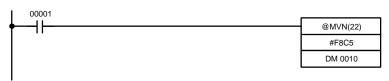

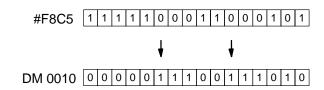

|     | 2-7-2    | MOVE NOT – MVN(22)                                 |

|     | 2-7-3    | DOUBLE MOVE – MOVL(—)                              |

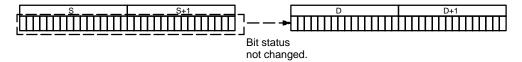

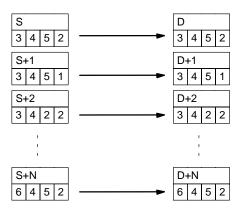

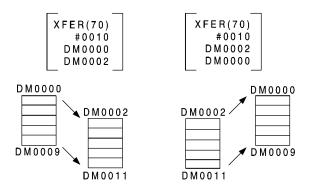

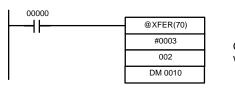

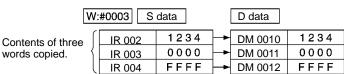

|     | 2-7-4    | BLOCK TRANSFER – XFER(70)                          |

|     | 2-7-5    | BLOCK SET – BSET(71)                               |

|     | 2-7-6    | DATA EXCHANGE – XCHG(73)                           |

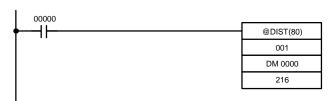

|     | 2-7-7    | SINGLE WORD DISTRIBUTE – DIST(80)                  |

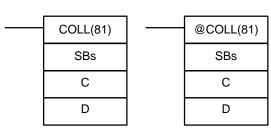

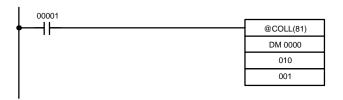

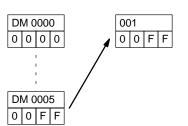

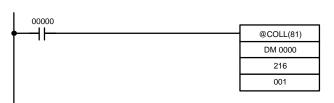

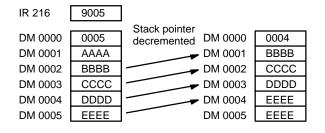

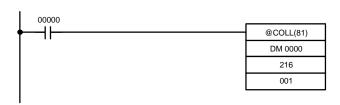

|     | 2-7-8    | DATA COLLECT – COLL(81)                            |

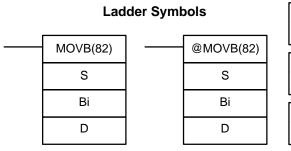

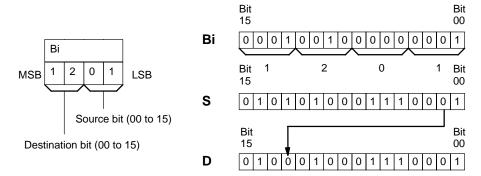

|     | 2-7-9    | MOVE BIT – MOVB(82)                                |

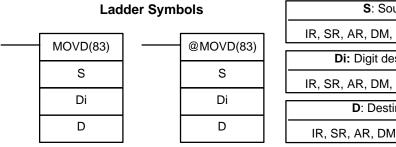

|     | 2-7-10   | MOVE DIGIT – MOVD(83)                              |

| 2-8  | Compar  | ison Instructions                         |

|------|---------|-------------------------------------------|

|      | 2-8-1   | COMPARE – CMP(20)                         |

|      | 2-8-2   | TABLE COMPARE – TCMP(85)                  |

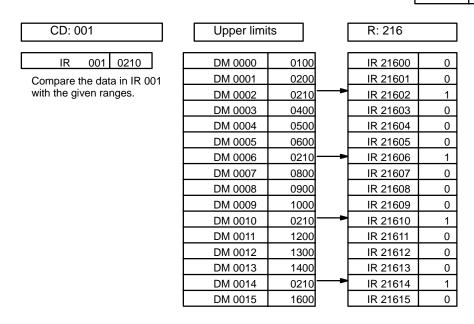

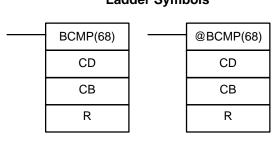

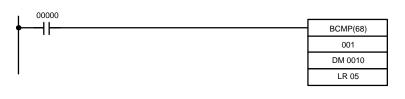

|      | 2-8-3   | BLOCK COMPARE – BCMP(68)                  |

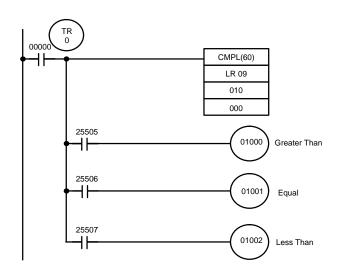

|      | 2-8-4   | DOUBLE COMPARE – CMPL(60)                 |

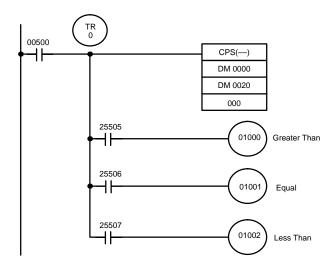

|      | 2-8-5   | SIGNED BINARY COMPARE – CPS(—)            |

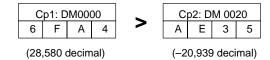

|      | 2-8-6   | DOUBLE SIGNED BINARY COMPARE – CPSL(—)    |

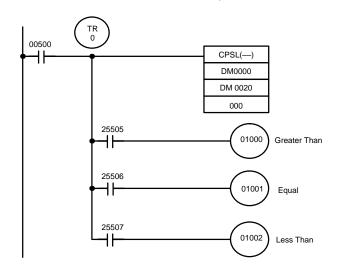

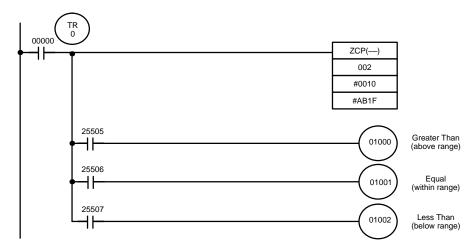

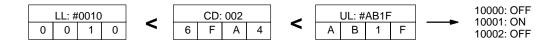

|      | 2-8-7   | AREA RANGE COMPARE – ZCP(—)               |

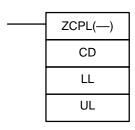

|      | 2-8-8   | DOUBLE AREA RANGE COMPARE – ZCPL(—)       |

| 2-9  |         |                                           |

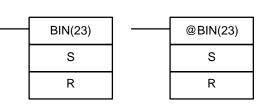

| 2-9  | 2-9-1   | sion Instructions BCD-TO-BINARY – BIN(23) |

|      | 2-9-1   |                                           |

|      |         | BINARY-TO-BCD – BCD(24)                   |

|      | 2-9-3   | DOUBLE BCD-TO-DOUBLE BINARY – BINL(58)    |

|      | 2-9-4   | DOUBLE BINARY-TO-DOUBLE BCD – BCDL(59)    |

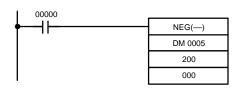

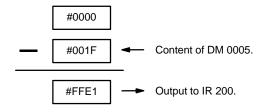

|      | 2-9-5   | 2'S COMPLEMENT – NEG(—)                   |

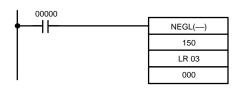

| 2 40 | 2-9-6   | DOUBLE 2'S COMPLEMENT – NEGL(—)           |

| 2-10 |         | ontrol Instructions                       |

|      | 2-10-1  | SCALING – SCL(66)                         |

|      |         | SIGNED BINARY TO BCD SCALING – SCL2(—)    |

|      |         | BCD TO SIGNED BINARY SCALING – SCL3(—)    |

|      |         | AVERAGE VALUE – AVG(—)                    |

| 2-11 | Special | Instructions                              |

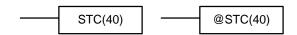

|      | 2-11-1  | SET CARRY – STC(40)                       |

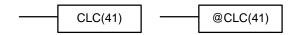

|      | 2-11-2  | CLEAR CARRY – CLC(41)                     |

| 2-12 | Symbol  | Math Instructions                         |

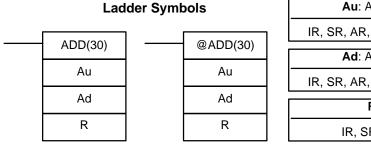

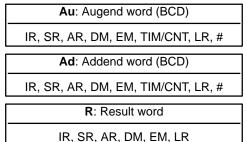

|      | 2-12-1  | BCD ADD – ADD(30)                         |

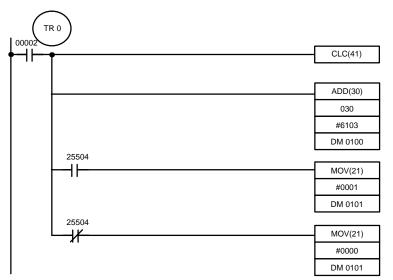

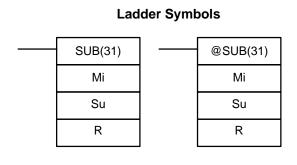

|      | 2-12-2  | BCD SUBTRACT – SUB(31)                    |

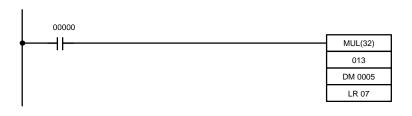

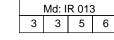

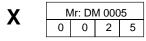

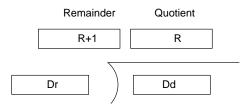

|      | 2-12-3  | BCD MULTIPLY – MUL(32)                    |

|      |         | BCD DIVIDE – DIV(33)                      |

|      |         | DOUBLE BCD ADD – ADDL(54)                 |

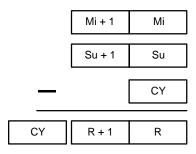

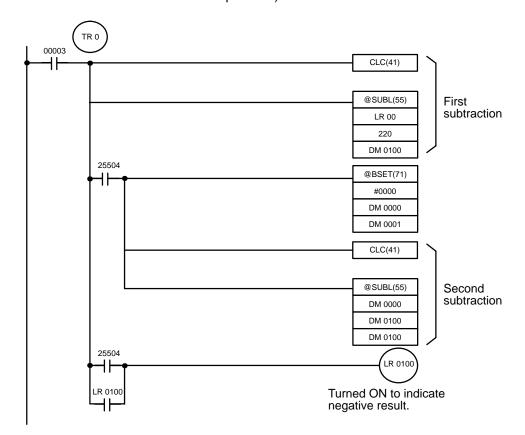

|      |         | DOUBLE BCD SUBTRACT – SUBL(55)            |

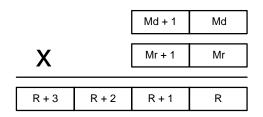

|      |         | DOUBLE BCD MULTIPLY – MULL(56)            |

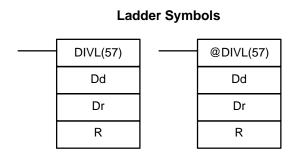

|      |         | DOUBLE BCD DIVIDE – DIVL(57)              |

|      |         | BINARY ADD – ADB(50)                      |

|      |         | BINARY SUBTRACT – SBB(51)                 |

|      |         | BINARY MULTIPLY – MLB(52)                 |

|      |         | BINARY DIVIDE – DVB(53)                   |

|      |         | DOUBLE BINARY ADD – ADBL(47)              |

|      |         | DOUBLE BINARY SUBTRACT – SBBL(48)         |

|      |         |                                           |

|      |         | SIGNED BINARY MULTIPLY – MBS(—)           |

|      |         | DOUBLE SIGNED BINARY MULTIPLY – MBSL(—)   |

|      |         | SIGNED BINARY DIVIDE – DBS(—)             |

|      |         | DOUBLE SIGNED BINARY DIVIDE – DBSL(—)     |

| 2-13 |         | ata Processing Instructions               |

|      |         | FIND MAXIMUM – MAX(—)                     |

|      |         | FIND MINIMUM – MIN(—)                     |

| 2-14 | -       | Math Instructions                         |

|      | 2-14-1  | ARITHMETIC PROCESS – APR(—)               |

|      | 2-14-2  | BIT COUNTER – BCNT(67)                    |

| 2-15 | _       | nstructions                               |

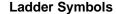

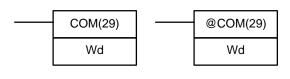

|      |         | COMPLEMENT – COM(29)                      |

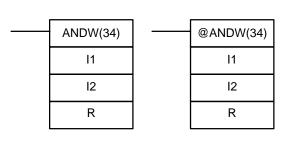

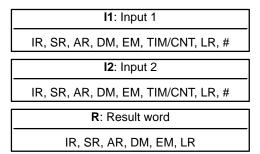

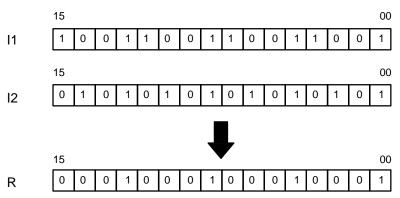

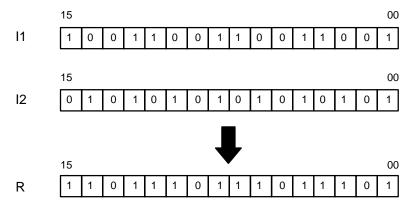

|      | 2-15-2  | LOGICAL AND – ANDW(34)                    |

|      |         | LOGICAL OR – ORW(35)                      |

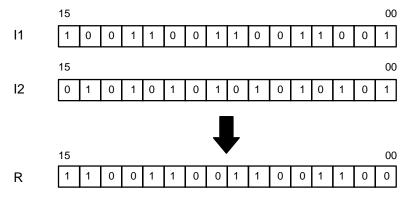

|      |         | EXCLUSIVE OR – XORW(36)                   |

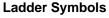

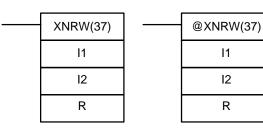

|      |         | EXCLUSIVE NOR – XNRW(37)                  |

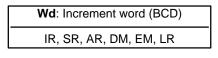

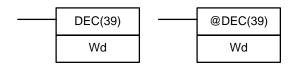

| 2-16 | 16 Increment/Decrement Instructions |                                                                                     |     |  |  |  |  |

|------|-------------------------------------|-------------------------------------------------------------------------------------|-----|--|--|--|--|

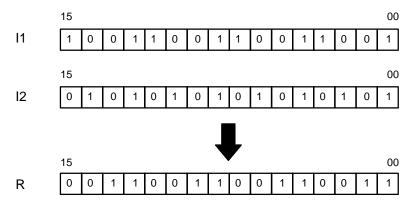

|      | 2-16-1                              | BCD INCREMENT – INC(38)                                                             | 95  |  |  |  |  |

|      | 2-16-2                              | BCD DECREMENT – DEC(39)                                                             | 96  |  |  |  |  |

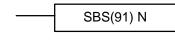

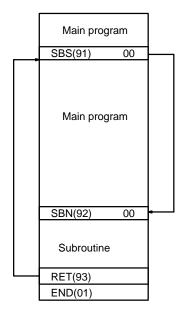

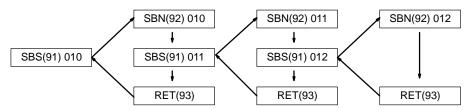

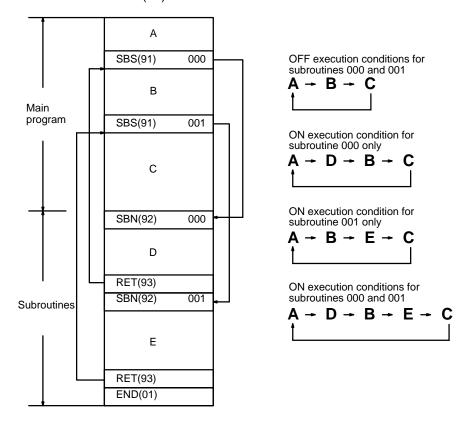

| 2-17 | Subrout                             | ine Instructions                                                                    | 96  |  |  |  |  |

|      | 2-17-1                              | SUBROUTINE ENTER – SBS(91)                                                          | 96  |  |  |  |  |

|      | 2-17-2                              | SUBROUTINE DEFINE and RETURN – SBN(92)/RET(93)                                      | 98  |  |  |  |  |

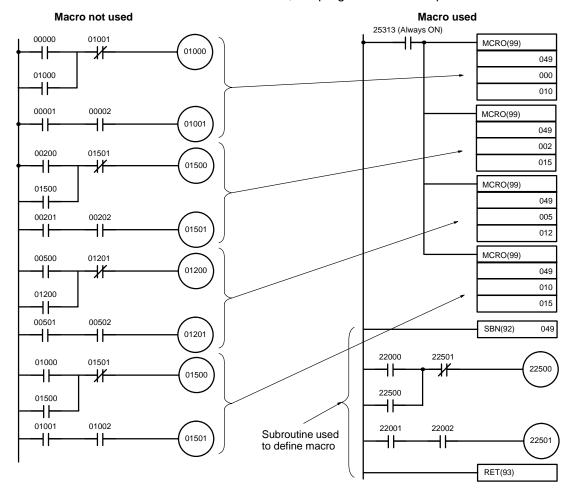

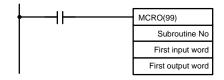

|      | 2-17-3                              | MACRO – MCRO(99)                                                                    | 99  |  |  |  |  |

| 2-18 | Interrup                            | t Control Instructions                                                              | 103 |  |  |  |  |

|      | 2-18-1                              | INTERRUPT CONTROL – INT(89)                                                         | 103 |  |  |  |  |

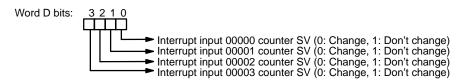

|      | 2-18-2                              | INTERVAL TIMER – STIM(69)                                                           | 104 |  |  |  |  |

| 2-19 | High-Sp                             | peed Counter/Pulse Output Instructions                                              | 107 |  |  |  |  |

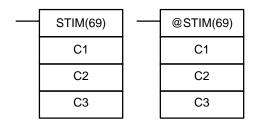

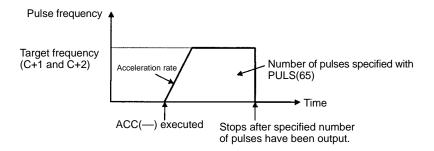

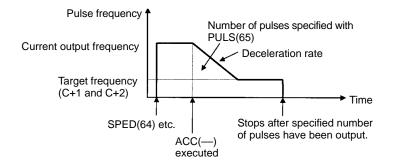

|      | 2-19-1                              | SET PULSES – PULS(65)                                                               | 107 |  |  |  |  |

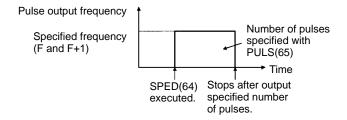

|      | 2-19-2                              | SPEED OUTPUT- SPED(64)                                                              | 110 |  |  |  |  |

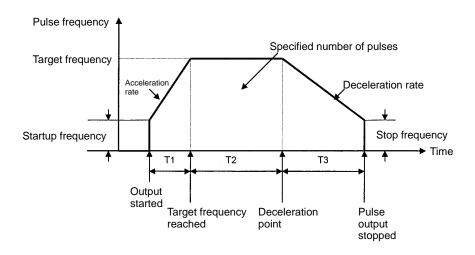

|      | 2-19-3                              | PULSE OUTPUT – PLS2(—)                                                              | 113 |  |  |  |  |

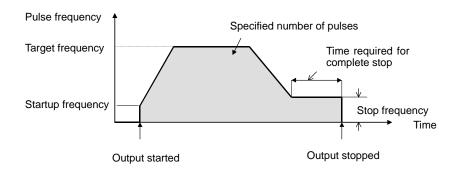

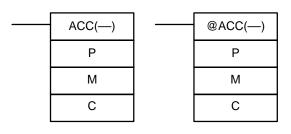

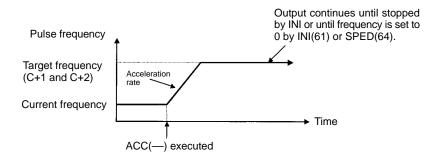

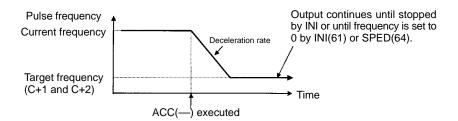

|      | 2-19-4                              | ACCELERATION CONTROL – ACC(—)                                                       | 117 |  |  |  |  |

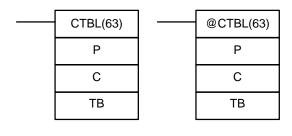

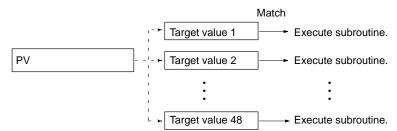

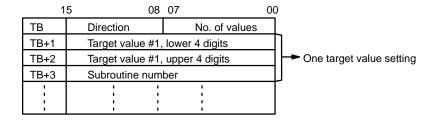

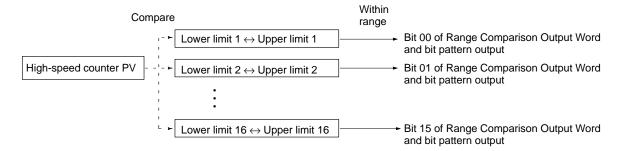

|      | 2-19-5                              | REGISTER COMPARISON TABLE – CTBL(63)                                                | 121 |  |  |  |  |

|      | 2-19-6                              | MODE CONTROL – INI(61)                                                              | 125 |  |  |  |  |

|      |                                     | HIGH-SPEED COUNTER PV READ – PRV(62)                                                | 127 |  |  |  |  |

| 2-20 | I/O Inst                            | ructions                                                                            | 128 |  |  |  |  |

|      | 2-20-1                              | I/O REFRESH – IORF(97)                                                              | 128 |  |  |  |  |

| 2-21 | Step Ins                            | structions: DEFINE and STEP START–STEP(08)/SNXT(09)                                 | 129 |  |  |  |  |

| 2-22 | <b>FAILUI</b>                       | ror Instructions:<br>RE ALARM AND RESET – FAL(06) and<br>E FAILURE ALARM – FALS(07) | 131 |  |  |  |  |

# 2-1 Instruction Tables

This section provides tables of the instructions available in the Customizable Counter Unit. The first two tables can be used to find instructions by function code. The last table can be used to find instructions by mnemonic.

# 2-1-1 Instructions with Fixed Function Codes

The following table lists the instructions that have fixed function codes. Each instruction is listed by mnemonic and by instruction name. Use the numbers in the leftmost column as the left digit and the number in the column heading as the right digit of the function code. The @ symbol indicates instructions with differentiated forms.

Expansion instructions without default function codes must be allocated function codes to enable using them. Even the expansion instructions with default function codes have been omitted from the following table and space has been provided so that you can write in the ones you will be using. Refer to the next page for details on expansion instructions.

| Left  | Right digit                              |                                     |                                    |                                  |                                               |                                        |                                          |                                     |                                                   |                                                   |

|-------|------------------------------------------|-------------------------------------|------------------------------------|----------------------------------|-----------------------------------------------|----------------------------------------|------------------------------------------|-------------------------------------|---------------------------------------------------|---------------------------------------------------|

| digit | 0                                        | 1                                   | 2                                  | 3                                | 4                                             | 5                                      | 6                                        | 7                                   | 8                                                 | 9                                                 |

| 0     | NOP<br>NO<br>OPERATION                   | END<br>END                          | IL<br>INTERLOCK                    | ILC<br>INTERLOCK<br>CLEAR        | JMP<br>JUMP                                   | JME<br>JUMP END                        | (@) FAL<br>FAILURE<br>ALARM AND<br>RESET | FALS<br>SEVERE<br>FAILURE<br>ALARM  | STEP<br>STEP<br>DEFINE                            | SNXT<br>STEP START                                |

| 1     | SFT<br>SHIFT<br>REGISTER                 | <b>KEEP</b><br>KEEP                 | CNTR<br>REVERS-<br>IBLE<br>COUNTER | DIFU<br>DIFFER-<br>ENTIATE UP    | DIFD<br>DIFFER-<br>ENTIATE<br>DOWN            | TIMH<br>HIGH-<br>SPEED<br>TIMER        | (@) WSFT<br>WORD<br>SHIFT                | (Expansion<br>Instruction)          | (Expansion<br>Instruction)                        | (Expansion<br>Instruction)                        |

| 2     | CMP<br>COMPARE                           | (@) MOV<br>MOVE                     | (@) MVN<br>MOVE NOT                | (@) BIN<br>BCD TO<br>BINARY      | (@) BCD<br>BINARY TO<br>BCD                   | (@) ASL<br>SHIFT LEFT                  | (@) ASR<br>SHIFT<br>RIGHT                | (@) ROL<br>ROTATE<br>LEFT           | (@) ROR<br>ROTATE<br>RIGHT                        | (@) COM<br>COMPLE-<br>MENT                        |

| 3     | (@) ADD<br>BCD ADD                       | (@) SUB<br>BCD<br>SUBTRACT          | (@) MUL<br>BCD<br>MULTIPLY         | (@) DIV<br>BCD<br>DIVIDE         | (@) ANDW<br>LOGICAL<br>AND                    | (@) ORW<br>LOGICAL OR                  | (@) XORW<br>EXCLUSIVE<br>OR              | (@) XNRW<br>EXCLUSIVE<br>NOR        | (@) INC<br>INCREMENT                              | (@) DEC<br>DECRE-<br>MENT                         |

| 4     | (@) STC<br>SET CARRY                     | (@) CLC<br>CLEAR<br>CARRY           |                                    |                                  |                                               |                                        |                                          | (Expansion<br>Instruction)          | (Expansion<br>Instruction)                        |                                                   |

| 5     | (@) ADB<br>BINARY ADD                    | (@) SBB<br>BINARY<br>SUBTRACT       | (@) MLB<br>BINARY<br>MULTIPLY      | (@) DVB<br>BINARY<br>DIVIDE      | (@) ADDL<br>DOUBLE<br>BCD ADD                 | (@) SUBL<br>DOUBLE<br>BCD<br>SUBTRACT  | (@) MULL<br>DOUBLE<br>BCD<br>MULTIPLY    | (@) DIVL<br>DOUBLE<br>BCD<br>DIVIDE | (@) BINL<br>DOUBLE<br>BCD-TO-<br>DOUBLE<br>BINARY | (@) BCDL<br>DOUBLE<br>BINARY-TO-<br>DOUBLE<br>BCD |

| 6     |                                          |                                     |                                    |                                  |                                               |                                        |                                          |                                     |                                                   |                                                   |

|       | (Expansion Instruction)                  | (Expansion Instruction)             | (Expansion Instruction)            | (Expansion Instruction)          | (Expansion Instruction)                       | (Expansion Instruction)                | (Expansion Instruction)                  | (Expansion Instruction)             | (Expansion Instruction)                           | (Expansion Instruction)                           |

| 7     | (@) XFER<br>BLOCK<br>TRANSFER            | (@) BSET<br>BLOCK SET               | (@) ROOT<br>SQUARE<br>ROOT         | (@) XCHG<br>DATA<br>EXCHANGE     | (@) SLD<br>ONE DIGIT<br>SHIFT LEFT            | (@) SRD<br>ONE DIGIT<br>SHIFT<br>RIGHT |                                          |                                     |                                                   |                                                   |

| 8     | (@) DIST<br>SINGLE<br>WORD<br>DISTRIBUTE | (@) COLL<br>DATA<br>COLLECT         | (@) MOVB<br>MOVE BIT               | (@) MOVD<br>MOVE DIGIT           | (@) SFTR<br>REVERS-<br>IBLE SHIFT<br>REGISTER | (@) TCMP<br>TABLE<br>COMPARE           |                                          | (Expansion<br>Instruction)          | (Expansion<br>Instruction)                        | (Expansion<br>Instruction)                        |

| 9     | (@) SEND<br>NETWORK<br>SEND              | (@) SBS<br>SUBROU-<br>TINE<br>ENTRY | SBN<br>SUBROU-<br>TINE<br>DEFINE   | RET<br>SUBROU-<br>TINE<br>RETURN |                                               |                                        |                                          | (@) IORF<br>I/O<br>REFRESH          |                                                   | (@) MCRO<br>MACRO                                 |

# 2-1-2 Expansion Instructions

The expansion instructions that can be used are listed below, along with the default function codes that are assigned when the Customizable Counter Unit is shipped.

| Name                           | Mnemonic           | Default function code |  |  |

|--------------------------------|--------------------|-----------------------|--|--|

| ASYNCHRONOUS<br>SHIFT REGISTER | ASFT               | 17                    |  |  |

| Not used.                      | FUN (See note 2.)  | 18                    |  |  |

| Not used.                      | FUN (See note 2.)  | 19                    |  |  |

| DOUBLE BINARY<br>ADD           | ADBL               | 47                    |  |  |

| DOUBLE BINARY<br>SUBTRACT      | SBBL               | 48                    |  |  |

| DOUBLE COMPARE                 | CMPL               | 60                    |  |  |

| MODE CONTROL                   | INI (See note 1.)  | 61                    |  |  |

| HIGH-SPEED<br>COUNTER PV READ  | PRV (See note 1.)  | 62                    |  |  |

| COMPARISON TABLE LOAD          | CTBL (See note 1.) | 63                    |  |  |

| SPEED OUTPUT                   | SPED (See note 1.) | 64                    |  |  |

| SET PULSES                     | PULS (See note 1.) | 65                    |  |  |

| SCALING                        | SCL                | 66                    |  |  |

| BIT COUNTER                    | BCNT               | 67                    |  |  |

| BLOCK COMPARE                  | BCMP               | 68                    |  |  |

| INTERVAL TIMER                 | STIM               | 69                    |  |  |

| DOUBLE 2'S<br>COMPLEMENT       | NEGL (See note 1.) | 87                    |  |  |

| Not used.                      | FUN (See note 2.)  | 88                    |  |  |

| INTERRUPT<br>CONTROL           | INT                | 89                    |  |  |

| Name a                           | M        | Defect                |

|----------------------------------|----------|-----------------------|

| Name                             | Mnemonic | Default function code |

| ACCELERATION CONTROL             | ACC      |                       |

| ARITHMETIC PROCESS               | APR      |                       |

| AVERAGE VALUE                    | AVG      |                       |

| SIGNED BINARY<br>COMPARE         | CPS      |                       |

| DOUBLE SIGNED<br>BINARY COMPARE  | CPSL     |                       |

| SIGNED BINARY DIVIDE             | DBS      |                       |

| DOUBLE SIGNED<br>BINARY DIVIDE   | DBSL     |                       |

| FIND MAXIMUM                     | MAX      |                       |

| SIGNED BINARY MUL-<br>TIPLY      | MBS      |                       |

| DOUBLE SIGNED<br>BINARY MULTIPLY | MBSL     |                       |

| FIND MINIMUM                     | MIN      |                       |

| DOUBLE MOVE                      | MOVL     |                       |

| 2'S COMPLEMENT                   | NEG      |                       |

| PULSE OUTPUT                     | PLS2     |                       |

| SIGNED BINARY TO BCD SCALING     | SCL2     |                       |

| BCD TO SIGNED BINARY SCALING     | SCL3     |                       |

| AREA RANGE COMPARE               | ZCP      |                       |

| DOUBLE AREA RANGE<br>COMPARE     | ZCPL     |                       |

Note

- 1. The default values depend on the model of the Customizable Counter Unit.

- 2. These instructions are supported by the CQM1H, but not by the Customizable Counter Unit. These instructions will be processed as NOPs if they are transferred to a Customizable Counter Unit.

# 2-1-3 Alphabetic List by Mnemonic

Dashes ("–") in the *Code* column indicate expansion instructions, which do not have fixed function codes. "None" indicates instructions for which function codes are not used. The @ symbol indicates instructions with differentiated forms.

| Mnemonic | Code | Words | Name                 | Page |

|----------|------|-------|----------------------|------|

| ACC (@)  |      | 4     | ACCELERATION CONTROL | 117  |

| ADB (@)  | 50   | 4     | BINARY ADD           | 76   |

| ADBL (@) | 47   | 4     | DOUBLE BINARY ADD    | 80   |

| ADD (@)  | 30   | 4     | BCD ADD              | 66   |

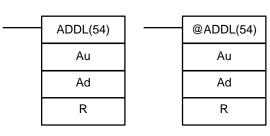

| ADDL (@) | 54   | 4     | DOUBLE BCD ADD       | 72   |

| AND      | None | 1     | AND                  | 10   |

| AND LD   | None | 1     | AND LOAD             | 11   |

| AND NOT  | None | 1     | AND NOT              | 10   |

| Mnemonic | Code | Words | Name                          | Page |

|----------|------|-------|-------------------------------|------|

| ANDW (@) | 34   | 4     | LOGICAL AND                   | 93   |

| APR (@)  | _    | 4     | ARITHMETIC PROCESS            | 89   |

| ASFT(@)  | 17   | 4     | ASYNCHRONOUS SHIFT REGISTER   | 31   |

| ASL (@)  | 25   | 2     | ARITHMETIC SHIFT LEFT         | 26   |

| ASR (@)  | 26   | 2     | ARITHMETIC SHIFT RIGHT        | 26   |

| AVG      |      | 4     | AVERAGE VALUE                 | 64   |

| BCD (@)  | 24   | 3     | BINARY TO BCD                 | 55   |

| BCDL (@) | 59   | 3     | DOUBLE BINARY-TO-DOUBLE BCD   | 56   |

| BCMP (@) | 68   | 4     | BLOCK COMPARE                 | 46   |

| BCNT (@) | 67   | 4     | BIT COUNTER                   | 92   |

| BIN (@)  | 23   | 3     | BCD-TO-BINARY                 | 54   |

| BINL (@) | 58   | 3     | DOUBLE BCD-TO-DOUBLE BINARY   | 55   |

| BSET (@) | 71   | 4     | BLOCK SET                     | 37   |

| CLC (@)  | 41   | 1     | CLEAR CARRY                   | 66   |

| CMP      | 20   | 3     | COMPARE                       | 44   |

| CMPL     | 60   | 4     | DOUBLE COMPARE                | 48   |

| CNT      | None | 2     | COUNTER                       | 20   |

| CNTR     | 12   | 3     | REVERSIBLE COUNTER            | 21   |

| COLL (@) | 81   | 4     | DATA COLLECT                  | 40   |

| COM (@)  | 29   | 2     | COMPLEMENT                    | 92   |

| CPS      |      | 4     | SIGNED BINARY COMPARE         | 49   |

| CPSL     |      | 4     | DOUBLE SIGNED BINARY COMPARE  | 50   |

| CTBL(@)  | 63   | 4     | COMPARISON TABLE LOAD         | 121  |

| DBS (@)  |      | 4     | SIGNED BINARY DIVIDE          | 85   |

| DBSL (@) |      | 4     | DOUBLE SIGNED BINARY DIVIDE   | 86   |

| DEC (@)  | 39   | 2     | BCD DECREMENT                 | 96   |

| DIFD     | 14   | 2     | DIFFERENTIATE DOWN            | 13   |

| DIFU     | 13   | 2     | DIFFERENTIATE UP              | 13   |

| DIST (@) | 80   | 4     | SINGLE WORD DISTRIBUTE        | 38   |

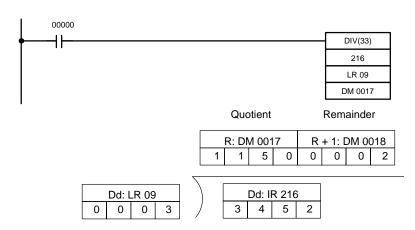

| DIV (@)  | 33   | 4     | BCD DIVIDE                    | 70   |

| DIVL (@) | 57   | 4     | DOUBLE BCD DIVIDE             | 75   |

| DVB (@)  | 53   | 4     | BINARY DIVIDE                 | 79   |

| END      | 01   | 1     | END                           | 14   |

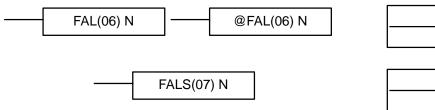

| FAL (@)  | 06   | 2     | FAILURE ALARM AND RESET       | 131  |

| FALS     | 07   | 2     | SEVERE FAILURE ALARM          | 131  |

| IL       | 02   | 1     | INTERLOCK                     | 15   |

| ILC      | 03   | 1     | INTERLOCK CLEAR               | 15   |

| INC (@)  | 38   | 2     | INCREMENT                     | 95   |

| INI (@)  | 61   | 4     | MODE CONTROL                  | 125  |

| INT (@)  | 89   | 4     | INTERRUPT CONTROL             | 103  |

| IORF (@) | 97   | 3     | I/O REFRESH                   | 128  |

| JME      | 05   | 2     | JUMP END                      | 17   |

| JMP      | 04   | 2     | JUMP                          | 17   |

| KEEP     | 11   | 2     | KEEP                          | 13   |

| LD       | None | 1     | LOAD                          | 10   |

| LD NOT   | None | 1     | LOAD NOT                      | 10   |

| MAX (@)  |      | 4     | FIND MAXIMUM                  | 87   |

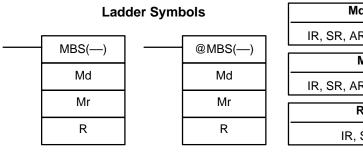

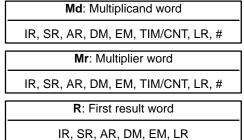

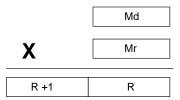

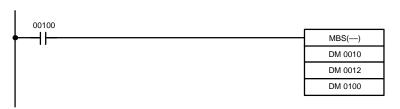

| MBS (@)  |      | 4     | SIGNED BINARY MULTIPLY        | 83   |

| MBSL (@) |      | 4     | DOUBLE SIGNED BINARY MULTIPLY | 84   |

| Mnemonic | Code | Words | Name                         | Page |

|----------|------|-------|------------------------------|------|

| MCRO (@) | 99   | 4     | MACRO                        | 99   |

| MIN (@)  |      | 4     | FIND MINIMUM                 | 88   |

| MLB (@)  | 52   | 4     | BINARY MULTIPLY              | 78   |

| MOV (@)  | 21   | 3     | MOVE                         | 32   |

| MOVB (@) | 82   | 4     | MOVE BIT                     | 42   |

| MOVD (@) | 83   | 4     | MOVE DIGIT                   | 43   |

| MOVL     |      | 4     | DOUBLE MOVE                  | 34   |

| MUL (@)  | 32   | 4     | BCD MULTIPLY                 | 69   |

| MULL (@) | 56   | 4     | DOUBLE BCD MULTIPLY          | 74   |

| MVN (@)  | 22   | 3     | MOVE NOT                     | 33   |

| NEG (@)  |      | 4     | 2'S COMPLEMENT               | 57   |

| NEGL (@) | 87   | 4     | DOUBLE 2'S COMPLEMENT        | 58   |

| NOP      | 00   | 1     | NO OPERATION                 | 14   |

| OR       | None | 1     | OR                           | 10   |

| OR LD    | None | 1     | OR LOAD                      | 11   |

| OR NOT   | None | 1     | OR NOT                       | 10   |

| ORW (@)  | 35   | 4     | LOGICAL OR                   | 93   |

| OUT      | None | 2     | OUTPUT                       | 11   |

| OUT NOT  | None | 2     | OUTPUT NOT                   | 11   |

| PLS2 (@) |      | 4     | PULSE OUTPUT                 | 113  |

| PRV (@)  | 62   | 4     | HIGH-SPEED COUNTER PV READ   | 127  |

| PULS (@) | 65   | 4     | SET PULSES                   | 107  |

| RET      | 93   | 1     | SUBROUTINE RETURN            | 98   |

| ROL (@)  | 27   | 2     | ROTATE LEFT                  | 27   |

| ROR (@)  | 28   | 2     | ROTATE RIGHT                 | 27   |

| RSET     | None | 2     | RESET                        | 12   |

| SBB (@)  | 51   | 4     | BINARY SUBTRACT              | 77   |

| SBBL (@) | 48   | 4     | DOUBLE BINARY SUBTRACT       | 81   |

| SBN      | 92   | 2     | SUBROUTINE DEFINE            | 98   |

| SBS (@)  | 91   | 2     | SUBROUTINE ENTRY             | 96   |

| SCL (@)  | 66   | 4     | SCALING                      | 59   |

| SCL2 (@) |      | 4     | SIGNED BINARY TO BCD SCALING | 60   |

| SCL3 (@) |      | 4     | BCD TO SIGNED BINARY SCALING | 62   |

| SET      | None | 2     | SET                          | 12   |

| SFT      | 10   | 3     | SHIFT REGISTER               | 24   |

| SFTR (@) | 84   | 4     | REVERSIBLE SHIFT REGISTER    | 29   |

| SLD (@)  | 74   | 3     | ONE DIGIT SHIFT LEFT         | 28   |

| SNXT     | 09   | 2     | STEP START                   | 129  |

| SPED (@) | 64   | 4     | SPEED OUTPUT                 | 110  |

| SRD (@)  | 75   | 3     | ONE DIGIT SHIFT RIGHT        | 29   |

| STC (@)  | 40   | 1     | SET CARRY                    | 66   |

| STEP     | 08   | 2     | STEP DEFINE                  | 129  |

| STIM (@) | 69   | 4     | INTERVAL TIMER               | 104  |

| SUB (@)  | 31   | 4     | BCD SUBTRACT                 | 67   |

| SUBL (@) | 55   | 4     | DOUBLE BCD SUBTRACT          | 73   |

| TCMP (@) | 85   | 4     | TABLE COMPARE                | 45   |

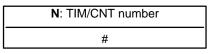

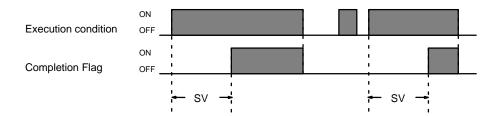

| TIM      | None | 2     | TIMER                        | 19   |

| TIMH     | 15   | 3     | HIGH-SPEED TIMER             | 22   |

| TMHH     |      | 3     | ONE-MS TIMER                 | 23   |

| Mnemonic | Code | Words | Name                      | Page |

|----------|------|-------|---------------------------|------|

| WSFT (@) | 16   | 3     | WORD SHIFT                | 25   |

| XCHG (@) | 73   | 3     | DATA EXCHANGE             | 38   |

| XFER (@) | 70   | 4     | BLOCK TRANSFER            | 35   |

| XNRW (@) | 37   | 4     | EXCLUSIVE NOR             | 95   |

| XORW (@) | 36   | 4     | EXCLUSIVE OR              | 94   |

| ZCP      |      | 4     | AREA RANGE COMPARE        | 52   |

| ZCPL     | _    | 4     | DOUBLE AREA RANGE COMPARE | 53   |

#### **Sequence Input Instructions** 2-2

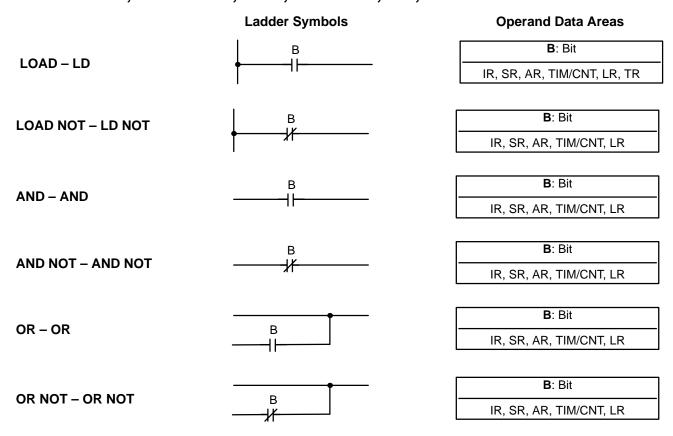

# 2-2-1 LOAD, LOAD NOT, AND, AND NOT, OR, and OR NOT

Limitations

There is no limit to the number of any of these instructions, or restrictions in the order in which they must be used, as long as the operands are in the appropriate address ranges.

Description

The status of the bit operand (B) assigned to LD or LD NOT determines the first execution condition. AND takes the logical AND between the execution condition and the status of its bit operand; AND NOT, the logical AND between the execution condition and the inverse of the status of its bit operand. OR takes the logical OR between the execution condition and the status of its bit operand; OR NOT, the logical OR between the execution condition and the inverse of the status of its bit operand.

**Flags**

There are no flags affected by these instructions.

# 2-2-2 AND LOAD and OR LOAD

AND LOAD - AND LD

00000 00002 **Ladder Symbol** 00001 00003

OR LOAD - OR LD

00000 00001 **Ladder Symbol** 00002 00003

Description

When instructions are combined into blocks that cannot be logically combined using only OR and AND operations, AND LD and OR LD are used. Whereas AND and OR operations logically combine a bit status and an execution condition, AND LD and OR LD logically combine two execution conditions, the current one and the last unused one.

In order to draw ladder diagrams, it is not necessary to use AND LD and OR LD instructions, nor are they necessary when inputting ladder diagrams directly, as is possible from the CX-Programmer. They are required, however, to convert the program to and input it in mnemonic form.

**Flags**

There are no flags affected by these instructions.

#### **Sequence Output Instructions** 2-3

There are seven instructions that can be used generally to control individual bit status. These are OUT, OUT NOT, DIFU(13), DIFD(14), SET, RSET, and KEEP(11). These instructions are used to turn bits ON and OFF in different ways.

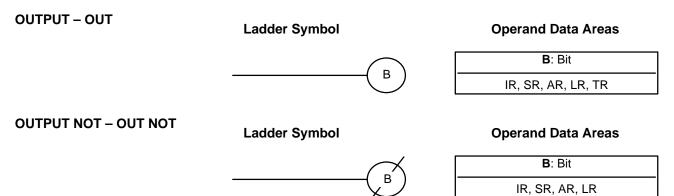

# 2-3-1 OUTPUT and OUTPUT NOT – OUT and OUT NOT

Limitations

Any output bit can generally be used in only one instruction that controls its sta-

Description

OUT and OUT NOT are used to control the status of the designated bit according to the execution condition.

OUT turns ON the designated bit for an ON execution condition, and turns OFF the designated bit for an OFF execution condition. With a TR bit, OUT appears at a branching point rather than at the end of an instruction line.

OUT NOT turns ON the designated bit for a OFF execution condition, and turns OFF the designated bit for an ON execution condition.

OUT and OUT NOT can be used to control execution by turning ON and OFF bits that are assigned to conditions on the ladder diagram, thus determining execution conditions for other instructions. This is particularly helpful and allows a complex set of conditions to be used to control the status of a single work bit, and then that work bit can be used to control other instructions.

The length of time that a bit is ON or OFF can be controlled by combining the OUT or OUT NOT with TIM. Refer to Examples under 2-5-1 TIMER - TIM for details.

#### **Flags**

There are no flags affected by these instructions.

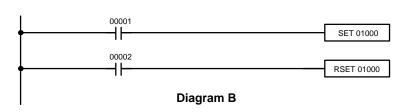

# 2-3-2 SET and RESET – SET and RSET

# **Ladder Symbols Operand Data Areas** B: Bit SET B IR, SR, AR, LR B: Bit RSET B IR, SR, AR, LR

#### Description

SET turns the operand bit ON when the execution condition is ON, and does not affect the status of the operand bit when the execution condition is OFF. RSET turns the operand bit OFF when the execution condition is ON, and does not affect the status of the operand bit when the execution condition is OFF.

The operation of SET differs from that of OUT because the OUT instruction turns the operand bit OFF when its execution condition is OFF. Likewise, RSET differs from OUT NOT because OUT NOT turns the operand bit ON when its execution condition is OFF.

#### **Precautions**

The status of operand bits for SET and RSET programmed between IL(02) and ILC(03), or JMP(04) and JME(05), will not change when the interlock or jump condition is met (i.e., when IL(02) or JMP(04) is executed with an OFF execution condition).

## **Flags**

There are no flags affected by these instructions.

# **Examples**

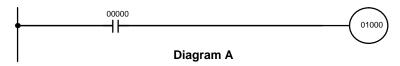

The following examples demonstrate the difference between OUT and SET/ RSET. In the first example (Diagram A), IR 01000 will be turned ON or OFF whenever IR 00000 goes ON or OFF.

In the second example (Diagram B), IR 01000 will be turned ON when IR 00001 goes ON and will remain ON (even if IR 00001 goes OFF) until IR 00002 goes ON.

| Address | Instruction | Operands |

|---------|-------------|----------|

| 00000   | LD          | 00000    |

| 00001   | OUT         | 01000    |

|   | Address | Instruction | Operands |

|---|---------|-------------|----------|

|   | 00000   | LD          | 00001    |

|   | 00001   | SET         | 01000    |

|   | 00002   | LD          | 00002    |

| j | 00003   | RSET        | 01000    |

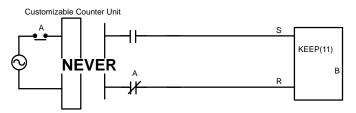

# 2-3-3 KEEP - KEEP(11)

# Ladder Symbol S KEEP(11) R

# Operand Data Areas B: Bit

IR, SR, AR, LR

Limitations

Any output bit can generally be used in only one instruction that controls its status.

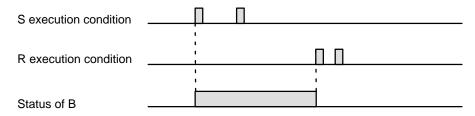

Description

KEEP(11) is used to maintain the status of the designated bit based on two execution conditions. These execution conditions are labeled S and R. S is the set input; R, the reset input. KEEP(11) operates like a latching relay that is set by S and reset by R.

When S turns ON, the designated bit will go ON and stay ON until reset, regardless of whether S stays ON or goes OFF. When R turns ON, the designated bit will go OFF and stay OFF until reset, regardless of whether R stays ON or goes OFF. The relationship between execution conditions and KEEP(11) bit status is shown below.

**Flags**

There are no flags affected by this instruction.

**Precautions**

Exercise caution when using a KEEP reset line that is controlled by an external normally closed device. Never use an input bit in an inverse condition on the reset (R) for KEEP(11) when the input device uses an AC power supply. The delay in shutting down the PC's DC power supply (relative to the AC power supply to the input device) can cause the designated bit of KEEP(11) to be reset. This situation is shown below.

Bits used in KEEP are not reset in interlocks. Refer to the 2-4-3 INTERLOCK – and INTERLOCK CLEAR IL(02) and ILC(03) for details.

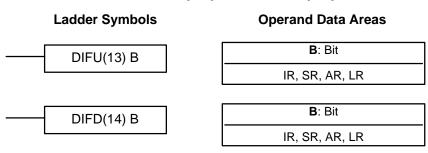

# 2-3-4 DIFFERENTIATE UP and DOWN – DIFU(13) and DIFD(14)

#### Limitations

Any output bit can generally be used in only one instruction that controls its status.

### **Description**

DIFU(13) and DIFD(14) are used to turn the designated bit ON for one cycle only.

Whenever executed, DIFU(13) compares its current execution with the previous execution condition. If the previous execution condition was OFF and the current one is ON, DIFU(13) will turn ON the designated bit. If the previous execution condition was ON and the current execution condition is either ON or OFF, DIFU(13) will either turn the designated bit OFF or leave it OFF (i.e., if the designated bit is already OFF). The designated bit will thus never be ON for longer than one cycle, assuming it is executed each cycle (see *Precautions*, below). Whenever executed, DIFD(14) compares its current execution with the previous execution condition. If the previous execution condition was ON and the current one is OFF, DIFD(14) will turn ON the designated bit. If the previous execution condition was OFF and the current execution condition is either ON or OFF, DIFD(14) will either turn the designated bit OFF or leave it OFF. The designated bit will thus never be ON for longer than one cycle, assuming it is executed each cycle (see *Precautions*, below).

These instructions are used when differentiated instructions (i.e., those prefixed with an @) are not available and single-cycle execution of a particular instruction is desired. They can also be used with non-differentiated forms of instructions that have differentiated forms when their use will simplify programming. Examples of these are shown below.

# **Flags**

There are no flags affected by these instructions.

#### **Precautions**

DIFU(13) and DIFD(14) operation can be uncertain when the instructions are programmed between IL and ILC, between JMP and JME, or in subroutines. Refer to 2-4-3 INTERLOCK and INTERLOCK CLEAR – IL(02) and ILC(03), 2-4-4 JUMP and JUMP END – JMP(04) and JME(05), 2-17 Subroutine Instructions, and 2-18-1 INTERRUPT CONTROL – INT(89).

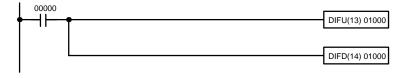

#### **Example**

In this example, IR 00100 will be turned ON for one cycle when IR 00000 goes from OFF to ON. IR 01000 will be turned ON for one cycle when IR 00000 goes from ON to OFF.

|   | Address | Instruction | Operands |

|---|---------|-------------|----------|

| ı | 00000   | LD          | 00000    |

| Ì | 00001   | DIFU(13)    | 01000    |

|   | 00002   | DIFD(14)    | 01000    |

# 2-4 Sequence Control Instructions

# 2-4-1 NO OPERATION - NOP(00)

#### Description

NOP(00) is not generally required in programming and there is no ladder symbol for it. When NOP(00) is found in a program, nothing is executed and the program execution moves to the next instruction. When memory is cleared prior to programming, NOP(00) is written at all addresses. NOP(00) can be input through the 00 function code.

#### **Flags**

There are no flags affected by NOP(00).

# 2-4-2 END - END(01)

# **Description**

END(01) is required as the last instruction in any program. If there are subroutines, END(01) is placed after the last subroutine. No instruction written after

END(01) will be executed. END(01) can be placed anywhere in the program to execute all instructions up to that point, as is sometimes done to debug a program, but it must be removed to execute the remainder of the program.

If there is no END(01) in the program, no instructions will be executed and the error message "NO END INST" will appear.

**Flags**

END(01) turns OFF the ER, CY, GR, EQ, LE, OF, and UF Flags.

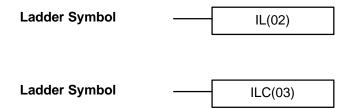

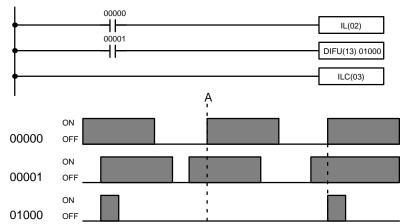

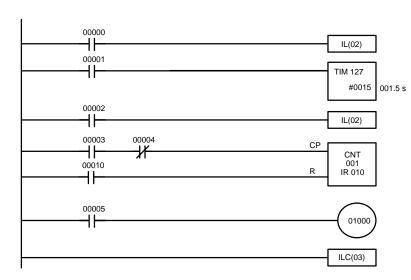

# 2-4-3 INTERLOCK and INTERLOCK CLEAR – IL(02) and ILC(03)

#### Description

IL(02) is always used in conjunction with ILC(03) to create interlocks. Interlocks are used to enable branching in the same way as can be achieved with TR bits, but treatment of instructions between IL(02) and ILC(03) differs from that with TR bits when the execution condition for IL(02) is OFF. If the execution condition of IL(02) is ON, the program will be executed as written, with an ON execution condition used to start each instruction line from the point where IL(02) is located through the next ILC(03).

If the execution condition for IL(02) is OFF, the interlocked section between IL(02) and ILC(03) will be treated as shown in the following table:

| Instruction                | Treatment                                                                                                                               |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| OUT and OUT NOT            | Designated bit turned OFF.                                                                                                              |

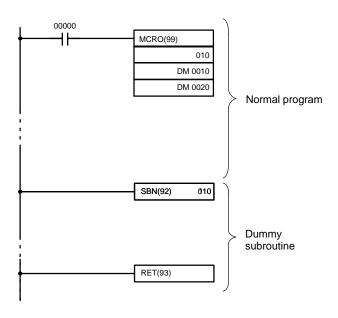

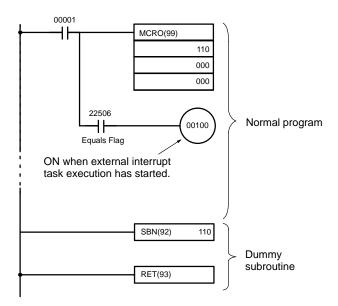

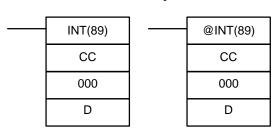

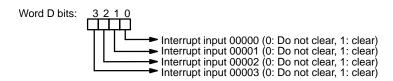

| TIM, TIMH(15), and TMHH(—) | Reset.                                                                                                                                  |